Intro

I graduated from Louisiana State University with a double major in Electrical Engineering and Computer Science in May 2020. I was privileged enough to be able to cultivate my software engineering skills working for Amazon, Chevron, and LSU physics dept (see work for details). While I still love programming, I discovered my passion for electrical engineering research working in the Applied Hybrid Electronic Materials & Structures (AHEMS) lab under Dr Daniels-Race in my final year at LSU.

I decided to pursue my hardware research interests at Georgia Tech with a master’s degree in Electrical and Computer Engineering. Over the 2021 summer, I gained valuable industry experience working on the DFT team at Apple. As for research opportunities, I found the Integrated Computational Electronics (ICE) Lab under Dr Hasler working on floating gates and analog computing. I initally joined the lab for a class credit to learn more about what they did. It was intriguing enough to me to center my master's thesis around it as well as caused me to pursue a PhD in the field.

Work

Apple

Physical Design Intern - Summer 2024

Cannot discuss project specifics but worked to improve PPA metrics by implementing optimization techniques across placement and CTS

Hardware Engineer Intern - Summer 2021

· Documented complex features of DFT verification environment for the DV team

· Implemented new testbench features at request of DV methodology team

· Converted the DFT-DV testbench to a simulator agnostic design by implementing support for another Verilog simulator

Amazon

Software Development Engineer Intern - Summer 2020

· Implemented an Audit trail into a massive customer facing application and worked across the full stack.

· This required setting up a new data store, creating backend functions, creating an internal API, working with many AWS resources, and pulling information from the API to display with typescript on a React website.

Software Development Engineer Intern - Summer 2019

· Built metrics dashboard from scratch in React with Elastic Search as a data store.

· Setup a data pipeline that used an internal wrapper on Elastic Map Reduce to aggregate billions of records and write to Kinesis FireHose which funneled into Elastic search.

Chevron

Software Engineering Intern - Summer 2018

· Automated deployment process of packages to Dev, QA and Prod servers using Git, Jenkins and PowerShell.

· Implemented and enhanced automated maintenance scripts for over 30+ servers using Jenkins and batch scripts.

Chevron

Software Engineering Intern - Summer 2017

· Applied knowledge of MYSQL in analyzing and extracting interface patterns between applications

· Using the interface patterns created a deployment plan for 30+ applications to a cloud service

Louisiana State University

Student Developer

· Using MYSQL, built and maintained various databases for several websites.

· Using HTML/CSS, built and maintained various websites for the physics department.

· Wrote PHP scripts to automatically populate various webpages from MYSQL databases.

Research

European Solid-State Electronics Research Conference (ESSERC)

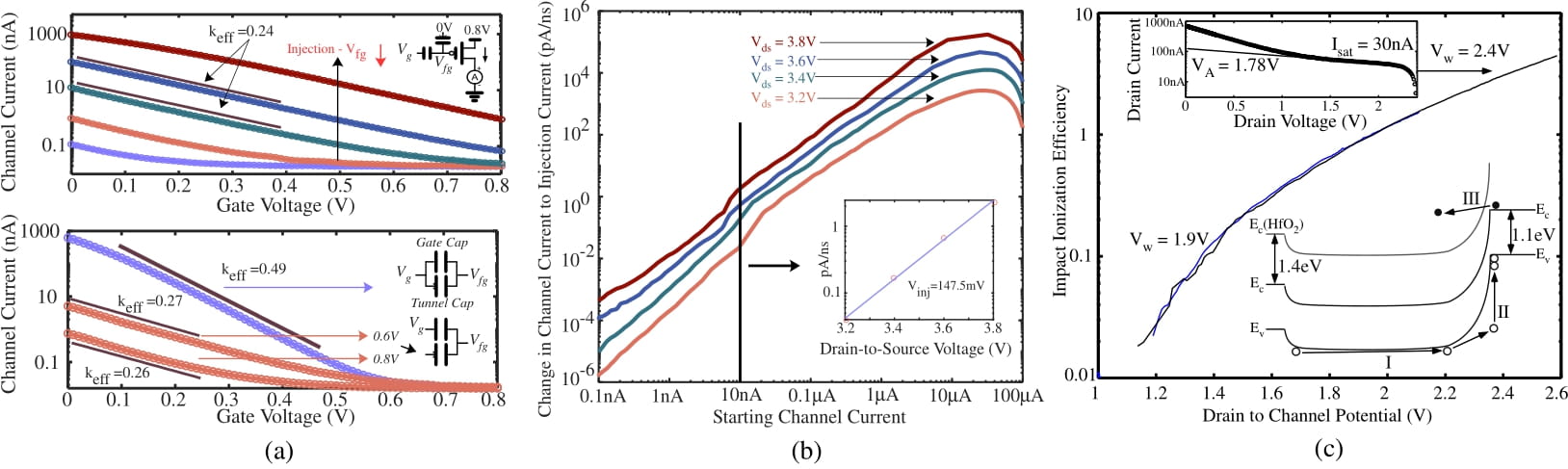

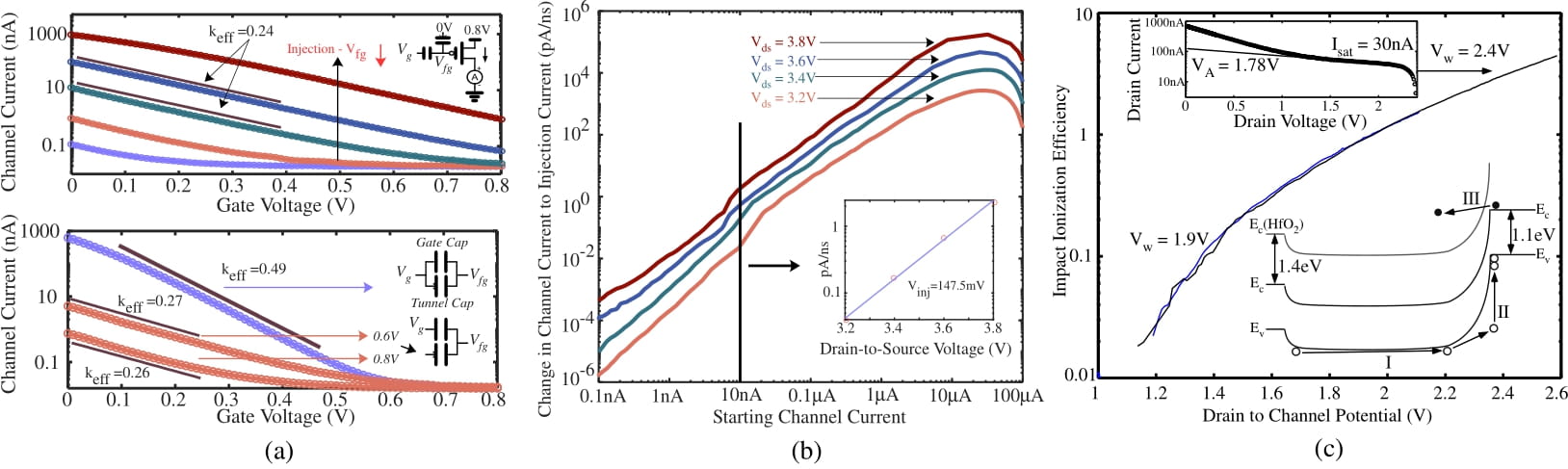

A 16nm pFET Floating Gate Transistor Enabling Programmable Analog Design in a FinFET Logic CMOS Process

Abstract: This work presents a 16nm pFET floating gate transistor that enables programmable analog design in a FinFET logic CMOS process. The device demonstrates the feasibility of extending floating gate technology to advanced FinFET nodes, opening new possibilities for programmable analog circuits in modern process technologies.

Link

Design, Automation & Test in Europe

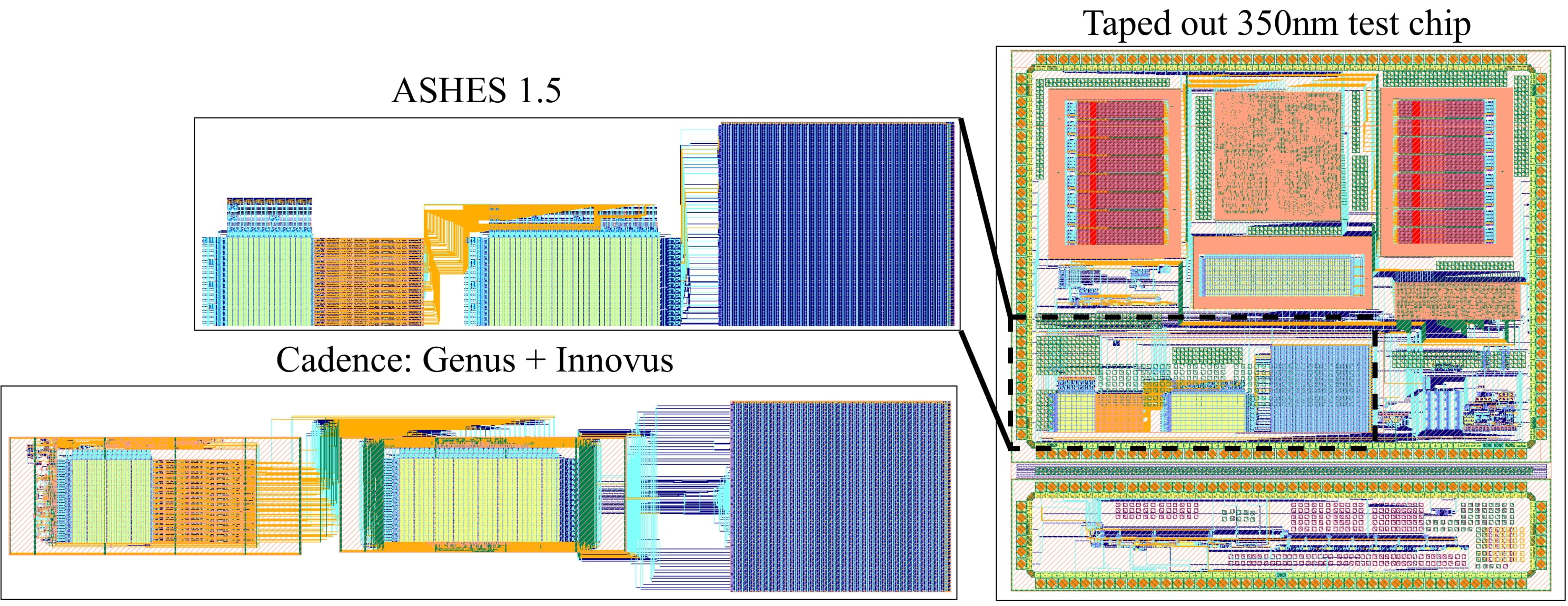

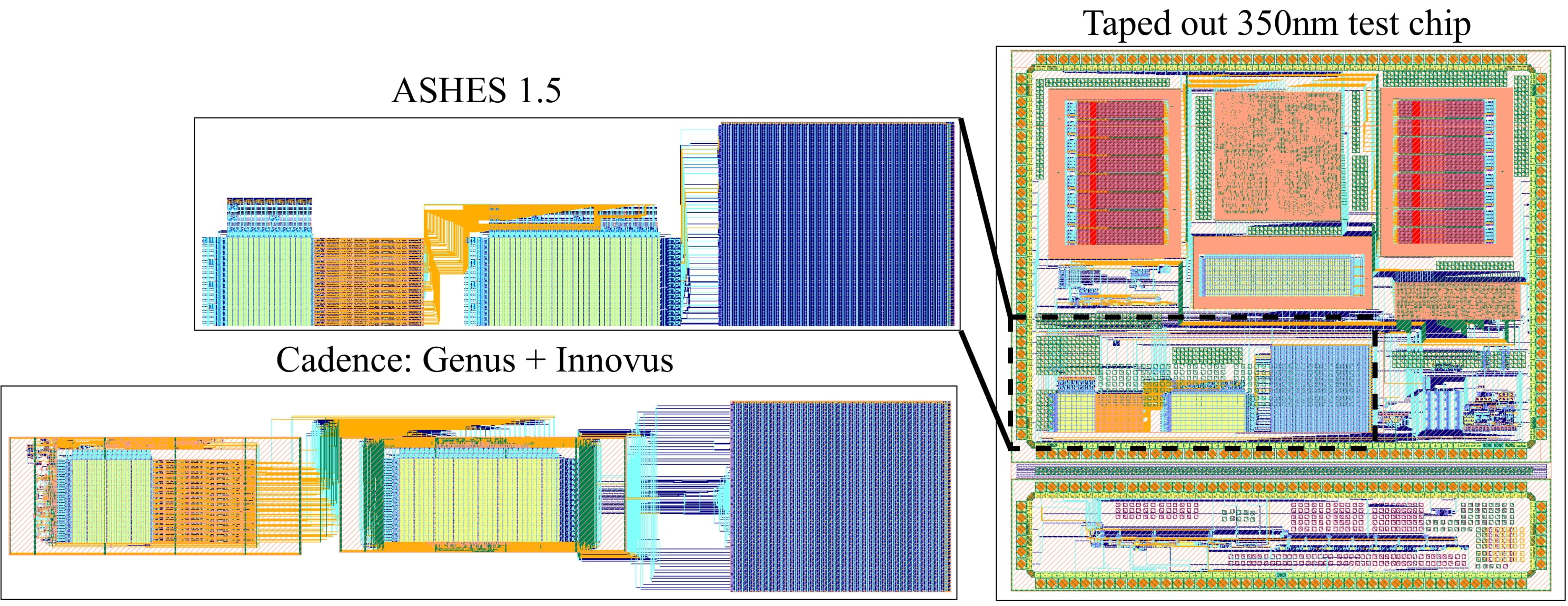

ASHES 1.5: Analog Computing Synthesis for FPAAs and ASICs

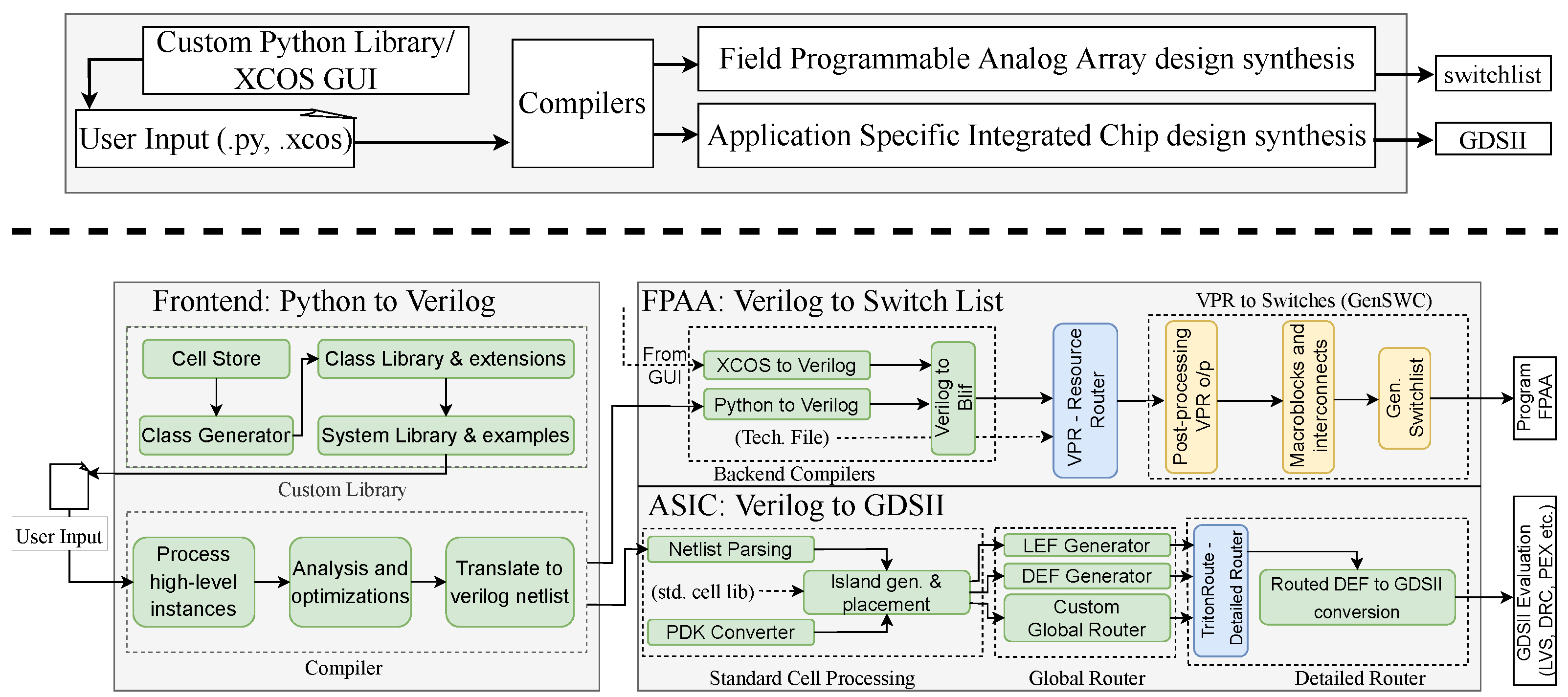

Abstract: This work presents ASHES 1.5, an updated analog high-level synthesis tool flow that enables automated design from high-level algorithmic descriptions to both Field Programmable Analog Arrays (FPAAs) and Application Specific Integrated Circuits (ASICs). The tool demonstrates significant improvements in analog computing synthesis capabilities for reconfigurable platforms.

Link

Opportunity Research Scholars Symposium 2025

Extending and Validating High Level Synthesis Tools for Analog Computing on Field Programmable Analog Arrays

Abstract: In this paper, we describe our efforts to extend and validate high-level synthesis tools for analog computing on field-programmable analog arrays (FPAAs). This work builds upon existing HLS infrastructure to provide improved design capabilities and validation methodologies for reconfigurable analog systems.

Link

Transactions on Very Large-Scale Integration

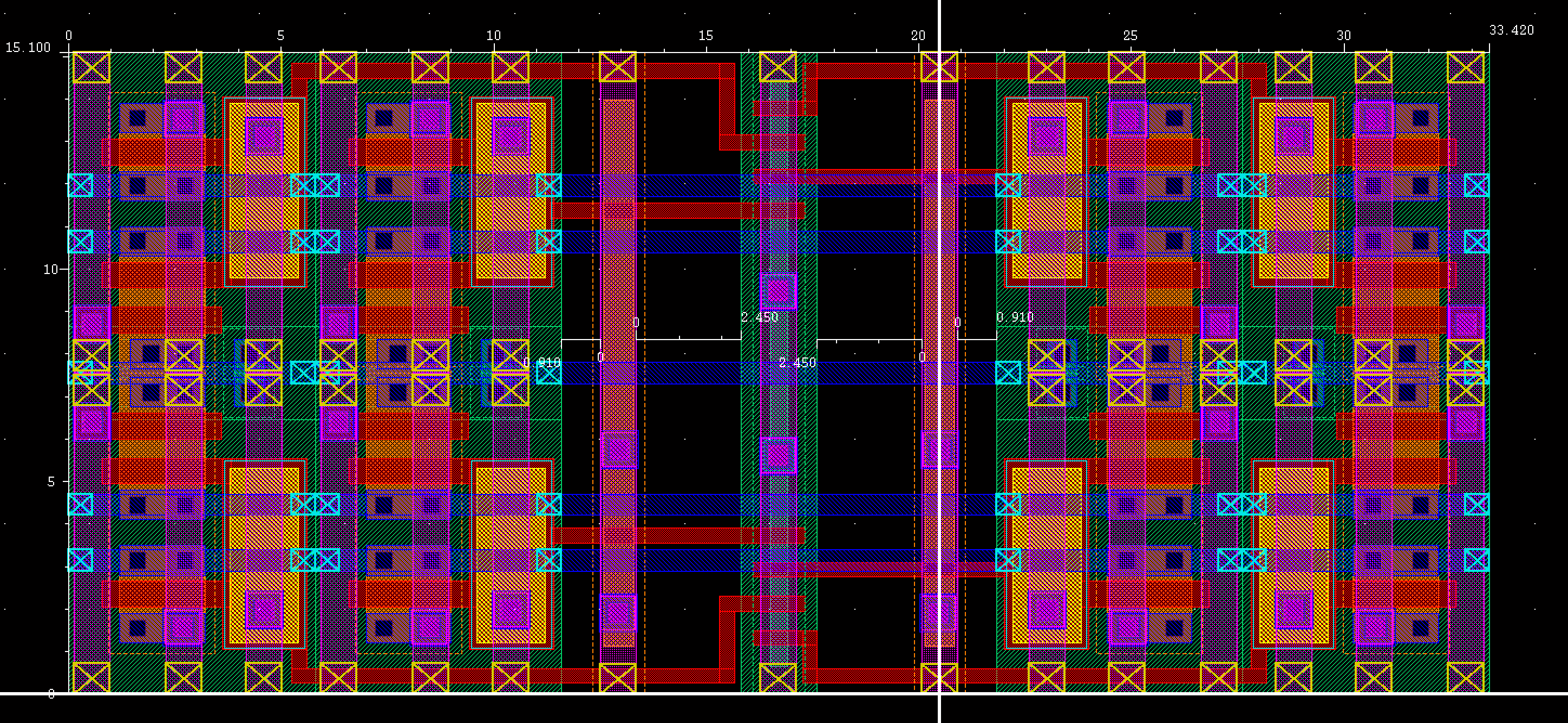

A 65 nm CMOS Analog Programmable Standard Cell Library for Mixed-Signal Computing

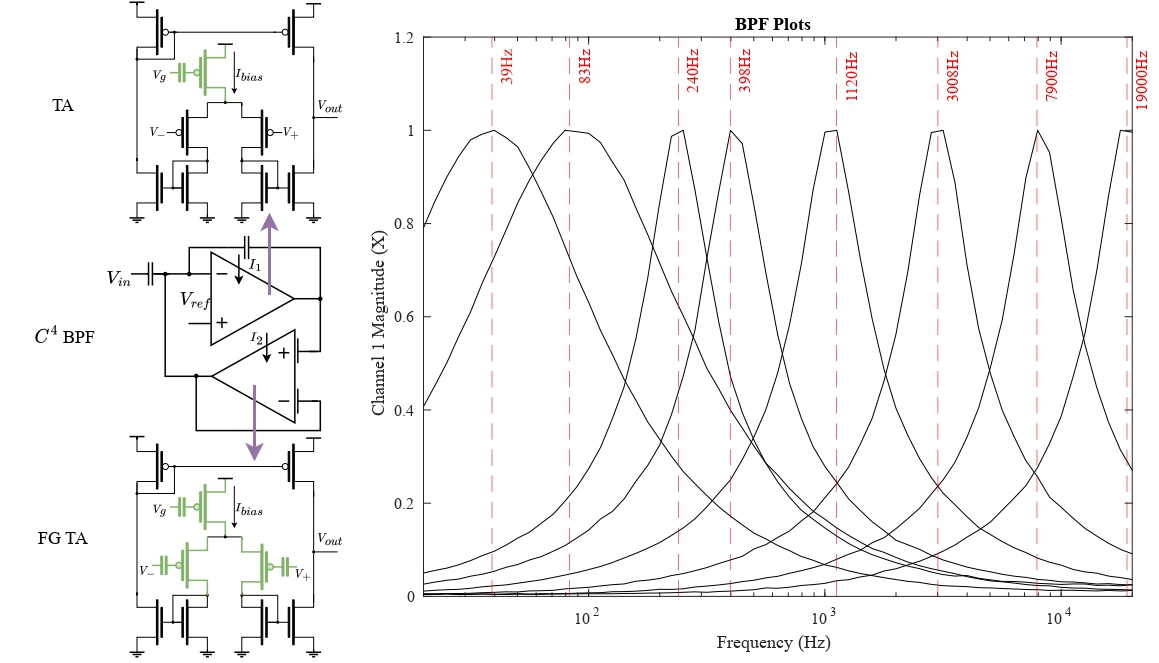

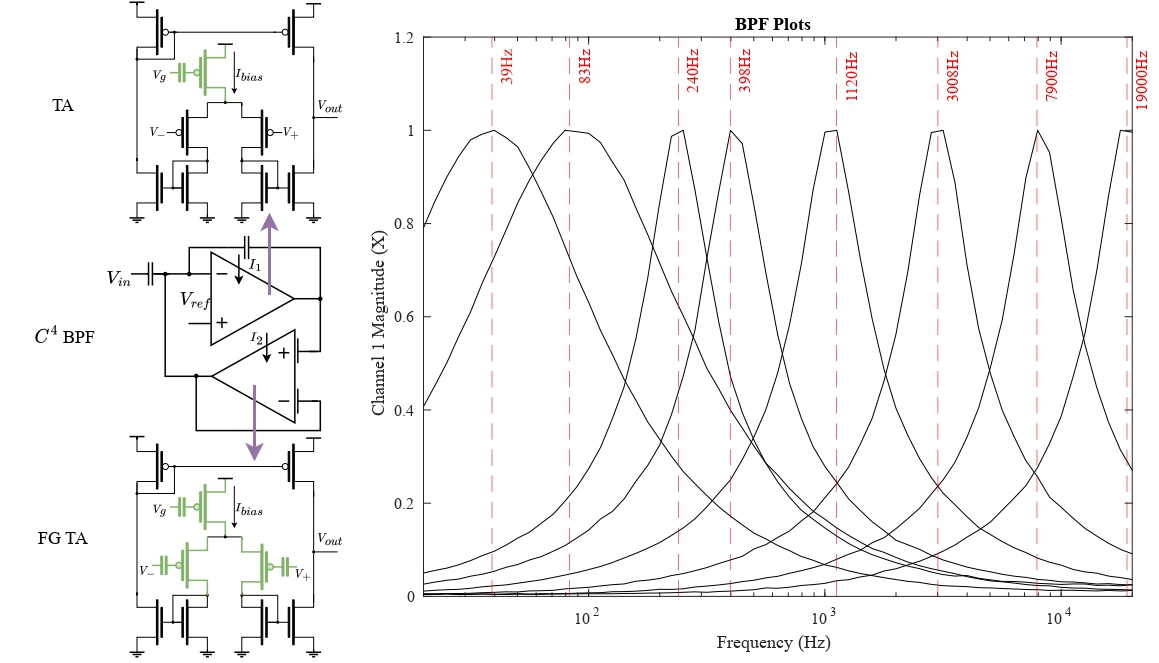

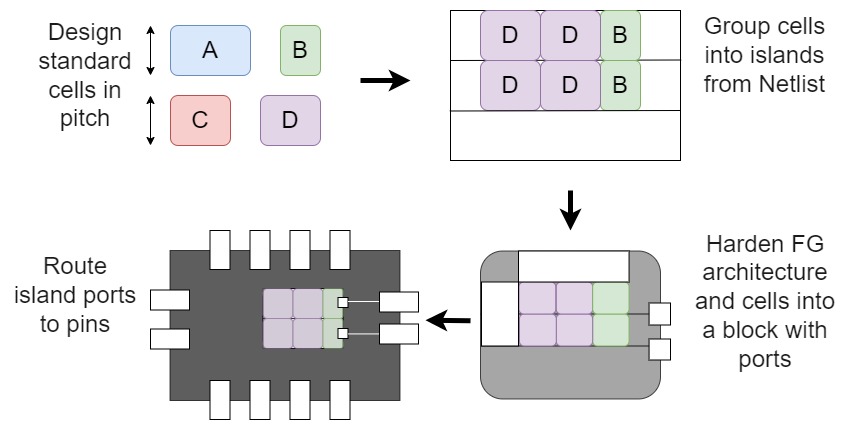

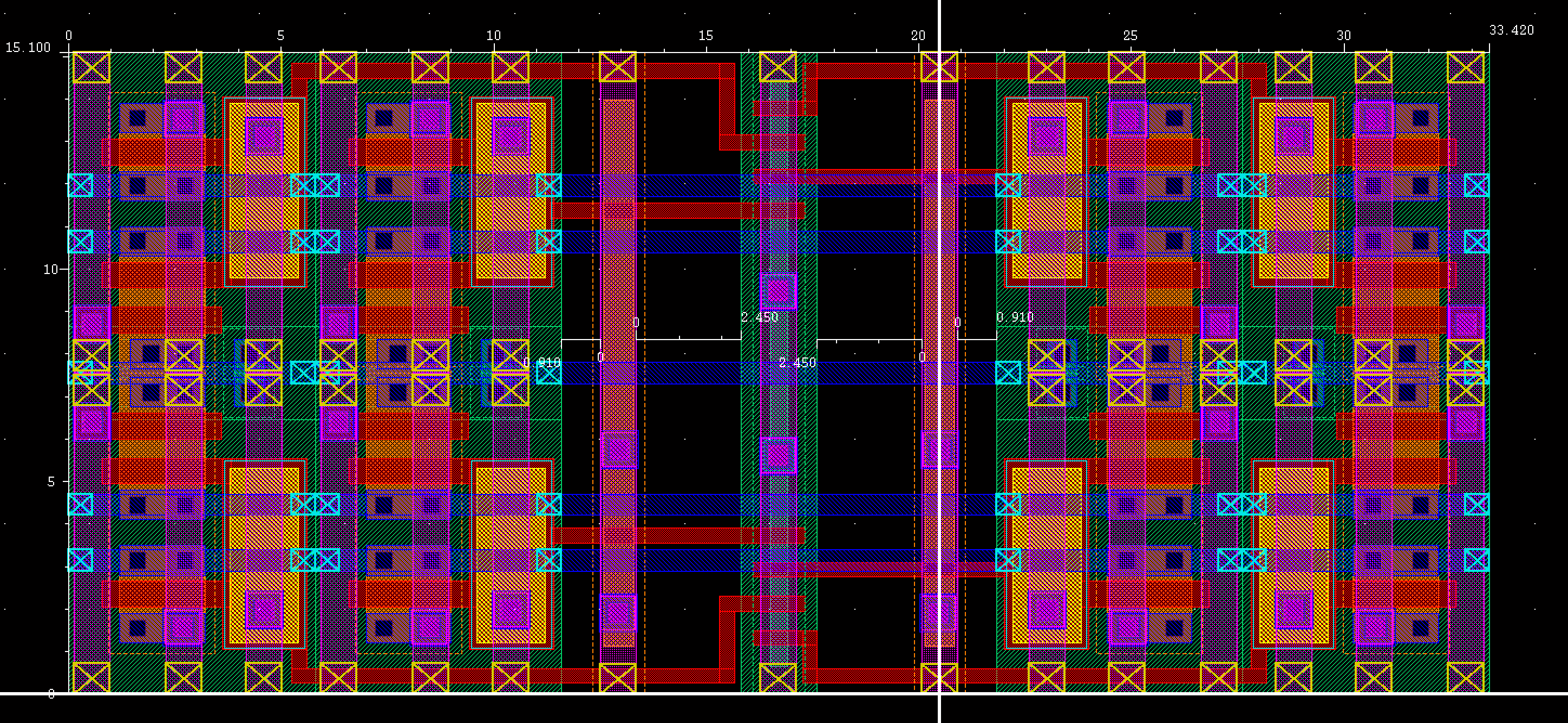

Abstract: Integrated circuit (IC) design for analog computing requires similar toolflows and synthesis as large-scale digital systems, in-turn necessitating a library of general-purpose analog cells. To this end, we present a programmable, floating-gate (FG)-based analog standard cell library in a commercially available 65 nm process that allows analog IC designers to use synthesis tools with an abstracted design mindset similar to large-scale digital design. We fabricate the test cells, which include filters with programmable corners, an analog classifier, and an arbitrary waveform generator (AWG); experimentally characterize FG programming; and experimentally demonstrate the performance of the standard cells. Overall, the standard cells achieve a similar or smaller footprint than previous approaches while leveraging the benefits of FG programming at smaller technology nodes.

Link

Transactions on Circuits and Systems I

A 130nm CMOS Programmable Analog Standard Cell Library

Abstract: This work presents an experimentally measured, implemented, openly-available programmable analog standard cell library in Skywater's 130nm CMOS process. Programmability enables standard-cell components, eliminating the need for large number of device geometries required in classic analog design. This effort presents the methodology in developing these analog standard cell library and integrating synthesis with these cells.

Link

Custom Integrated Circuits Conference

A 65nm and 130nm CMOS programmable analog standard cell library for scalable system synthesis

Abstract: Analog IC design for analog computing requires a similar toolflow and synthesis as large-scale digital. Analog synthesis to custom IC design requires an analog standard cell library that builds upon the experience and synthesis of large-scale Field Programmable Analog Arrays (FPAA). This effort presents the first programmable analog standard cell library, where Floating-Gate (FG) devices in standard CMOS provide the high precision (e.g. 14bit) programmability across multiple process nodes. A single library, developed in both 65nm CMOS and Skywater (open-source) 130nm CMOS, facilitates high-level synthesis, enabling the creation of versatile analog computing applications that are adaptable across various process nodes. Programmability is essential to have a moderate number of cells cover a wide space of analog computing and system design.

Link

Opportunity Research Scholars Symposium 2024

Analog HighLevel Synthesis for Field Programmable Analog Arrays

Best Paper Runner up

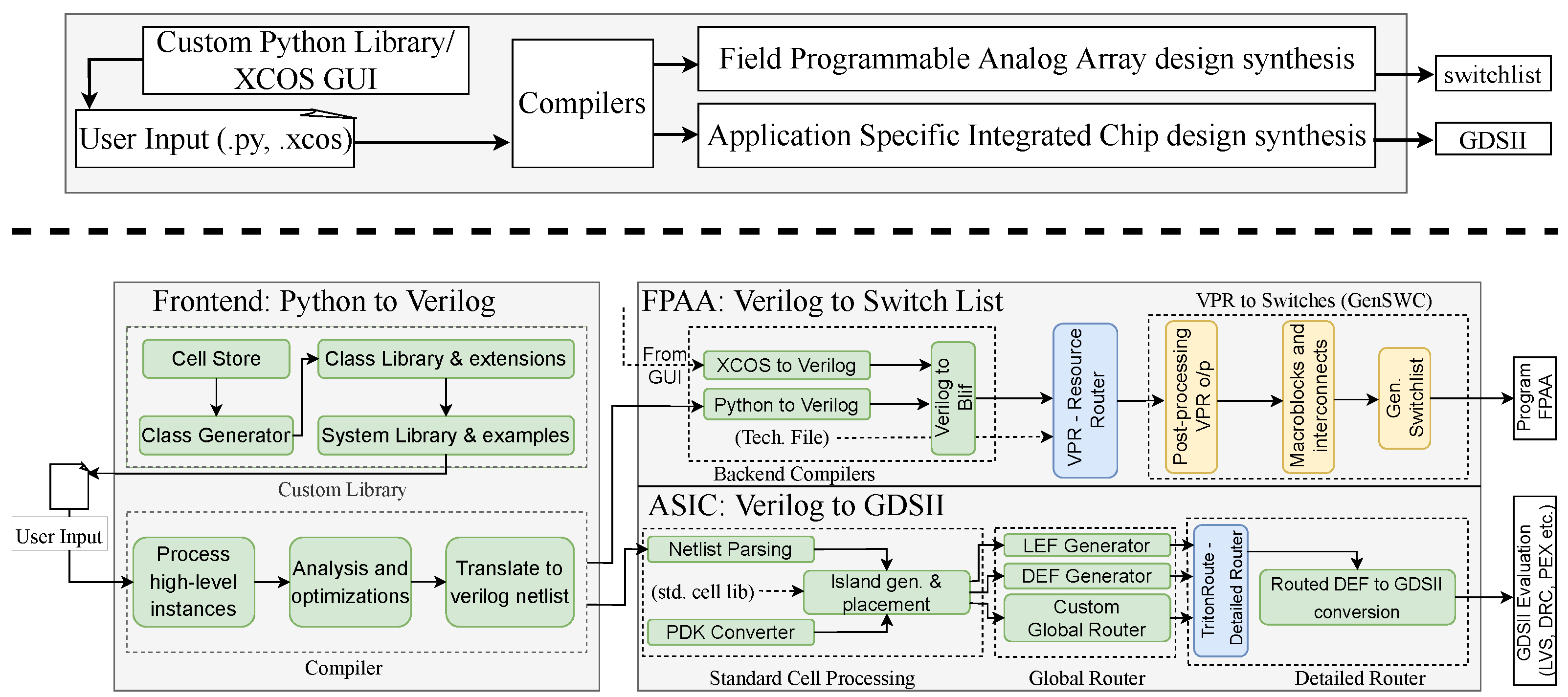

Abstract: In this paper, we describe our effort to extend the development of a standard framework for analog computing through further developing and integrating an existing high level synthesis (HLS) tool for analog system design. These Python and Scilab based tools allow designers to design and implement reconfigurable systems on field-programmable analog arrays (FPAA). In doing this, we can provide a way to have the same ease of development that digital integrated circuits (ICs) have with the field-programmable gate-array (FPGA). We describe the importance of analog computing, the state of the old tool flow, our contributions to upgrading the tool flow, and our demonstration of the working tools.

Paper Link

J. Low Power Electron. Appl.

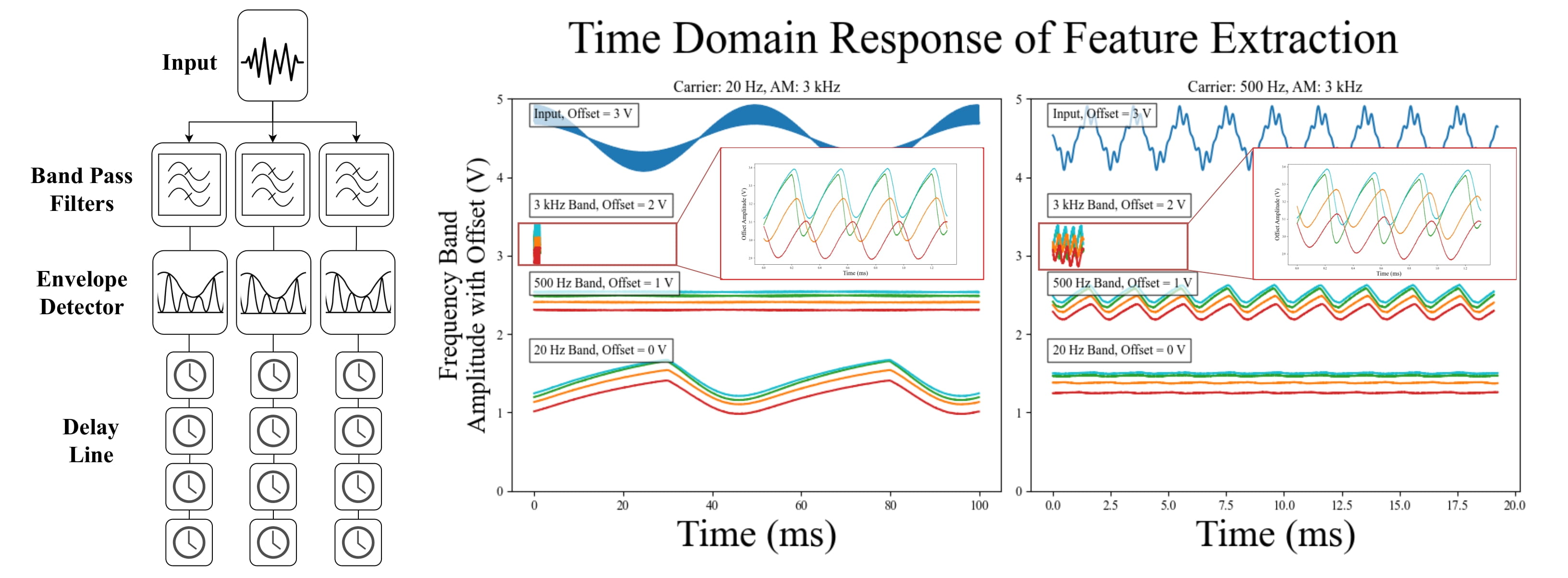

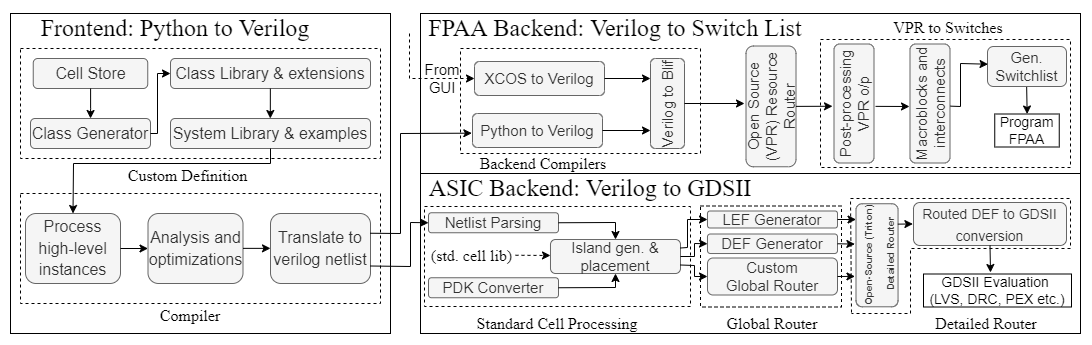

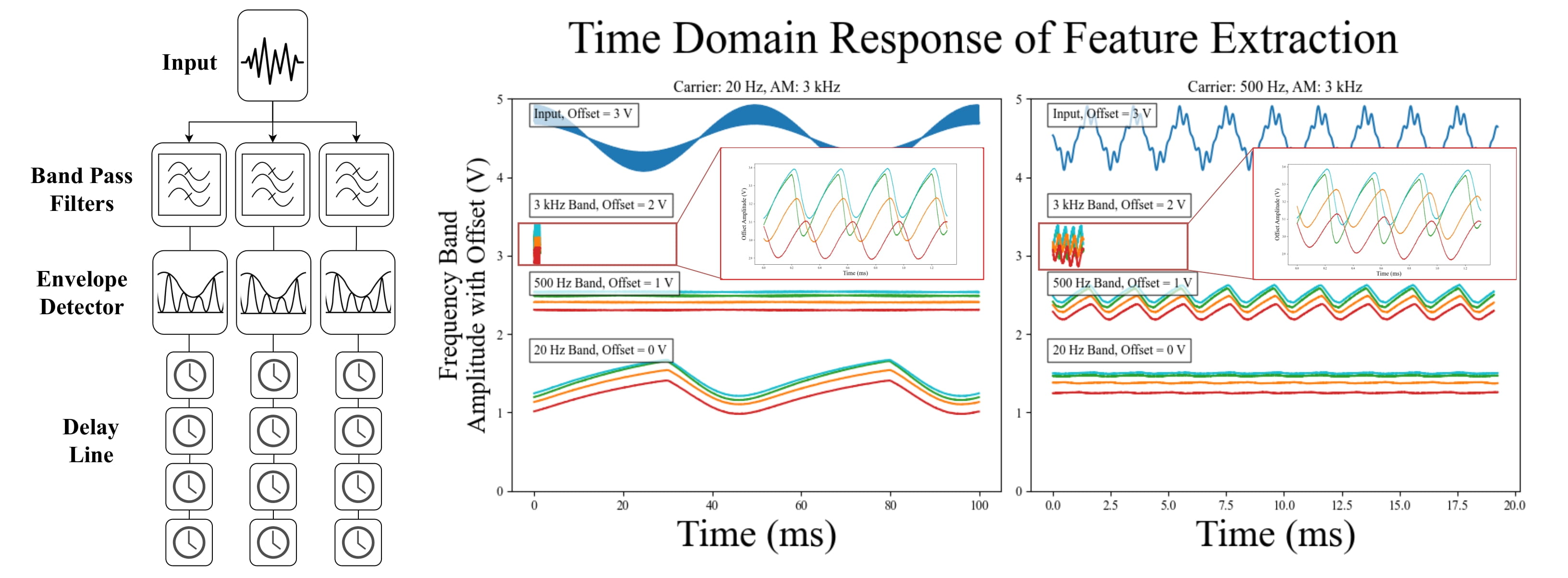

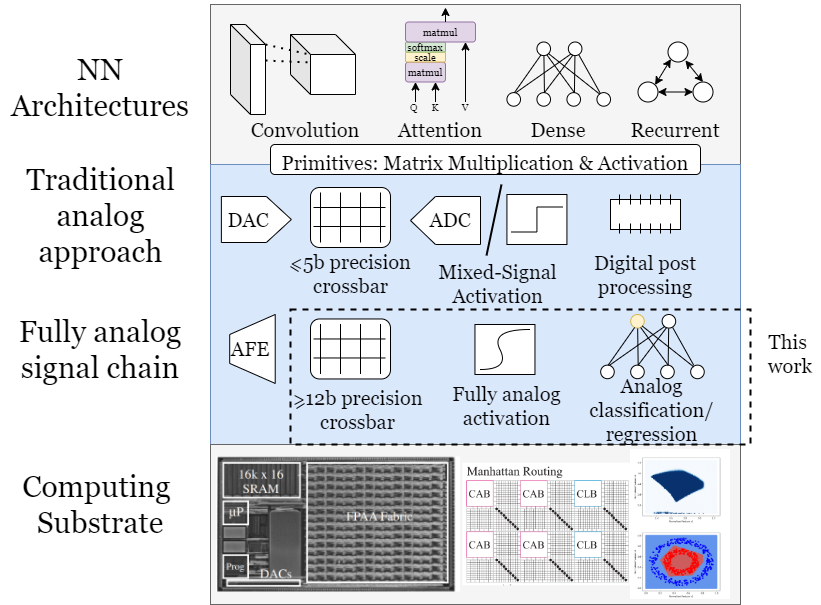

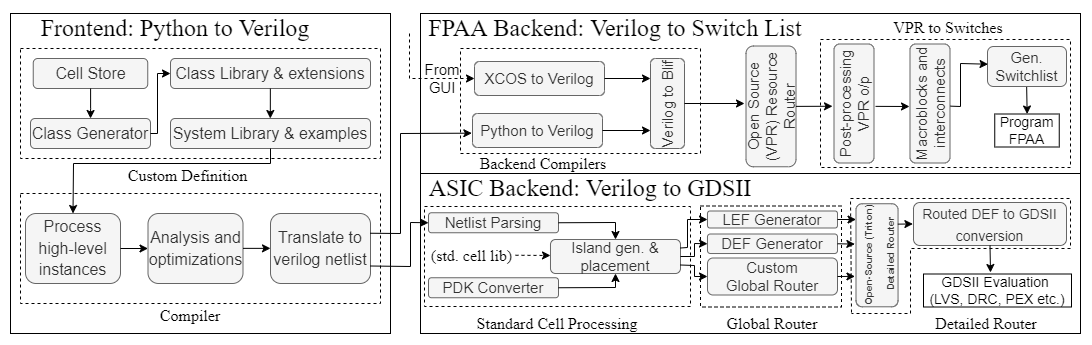

Analog System High-Level Synthesis for Energy-Efficient Reconfigurable Computing

Abstract: The design of analog computing systems requires significant human resources and domain expertise due to the lack of automation tools to enable these highly energy-efficient, high-performance computing nodes. This work presents the first automated tool flow from a high-level representation to a reconfigurable physical device. This tool begins with a high-level algorithmic description, utilizing either our custom Python framework or the XCOS GUI, to compile and optimize computations for integration into an Integrated Circuit (IC) design or a Field Programmable Analog Array (FPAA). An energy-efficient embedded speech classifier benchmark illustrates the tool demonstration, automatically generating GDSII layout or FPAA switch list targeting.

Link

Midwest Circuits and Systems

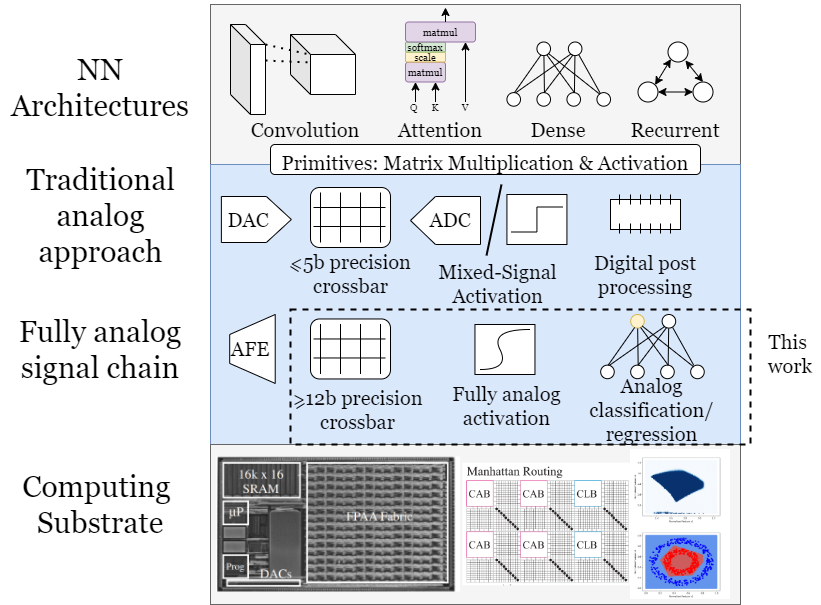

Efficient Implementation of a Fully Analog Neural Network on a Reconfigurable Platform

Conference Abstract: This paper investigates the potential of floating gate field-effect transistors (FETs) as primitives for subthreshold computation in analog neural networks. By leveraging the inherent properties of these transistors, we demonstrate their suitability for constructing neural network activation functions, such as sigmoid and rectified linear units (ReLUs), as well as winner-take-all (WTA) circuits for softmax activation. Our end-to-end analog implementation successfully classifies the concentric circles problem, illustrating the advantages of maintaining an analog signal chain throughout the process.

Slides Paper Poster Link

Design Automation Conference

ASHeS: Analog System High-level Synthesis for Reconfigurable Computing

Accepted as a work-in-progress poster at the 60th DAC conference, This work presents the first automated tool flow from a high-level representation to a reconfigurable physical device. This tool starts from a high-level algorithmic description either from a custom python library or XCOS GUI to compile and lower the computation to either an Application Specific Integrated Circuit (ASIC) design or a Field Programmable Analog Array (FPAA).

Poster

CRNCH Fellowship

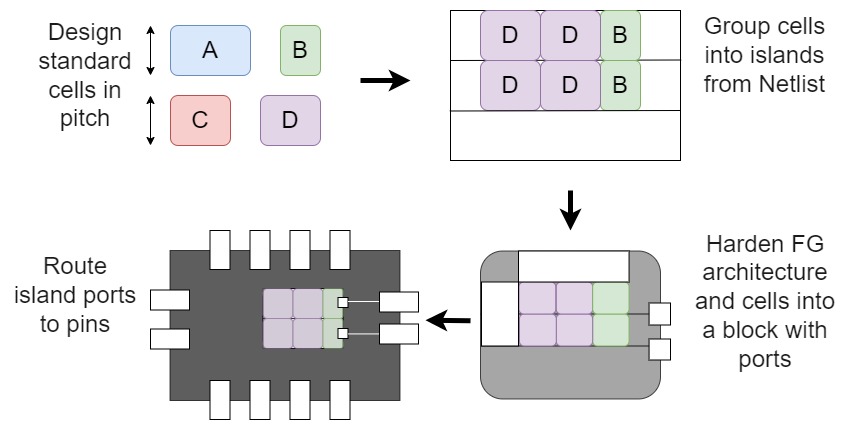

Automated Synthesis for Analog Computing Systems

Selected for the Fall 2022 CRNCH fellowship, this project proposes a Floating Gate (FG) architecture-aware synthesis tool that generates GDSII layout from analog standard cells and a netlist description. The outcomes of the work will be an open source tool that enables rapid creation of Application Specific Integrated Chips (ASIC) layout, a PDK conversion utility and FG standard cells across multiple process nodes.

Proposal

Master's Thesis

Analog Standard Cell Libraries

A standard cell is a level of abstraction that creates logical circuit building blocks that can be assembled to build complex architectures. The concept of abstraction using standard cells is a well-established notion in digital architecture. In fact, productivity of digital designers has been greatly supported by these cells, yet there isn't any widespread equivalent in the analog domain. Generally, due to the large number of design parameters that tend to change across process nodes, it has not been viewed as a worthwhile endeavor to create analog standard cells without reconfigurability of those parameters. This work aims to show how leveraging floating gates can create abstractable analog circuits which build into standard cells that enable large-scale, low power, mixed signal, systems-on-chip.

Thesis